# 特集/ナノテク実用化の鍵を握るナノ粒子の制御と応用

# 微結晶粒子のドライプロセスによる 電子セラミックス厚膜の形成と応用

# Preparation of Electronic Ceramic Dick Layer of Fine Particle Crystalline by Dry Process and Its Application

井上 光輝 <sup>a)</sup>,申 光鎬 <sup>b)</sup> Mitsuteru INOUE, Ph.D., Kanho SHIN, Ph.D.

## 豊橋技術科学大学

Toyohashi University of Technology a) 教授 Professor, b) 助教授 Associate Professor

# 1. はじめに

情報技術の進展に伴い、電子セラミックス厚膜が重要な基盤材料となっている。例えば、MEMS技術によるマイクロアクチュエータや、光・高周波デバイスなどで、数 $\mu$ mから数百 $\mu$ mの厚さをもつ良質な圧電セラミックス材料や強磁性セラミックス材料が要求されている。よく知られているように、 $1\mu$ m程度までの厚さをもつ電子セラミックス薄膜は、スパッタリングやCVD法などの物理・化学成膜法で高品位な薄膜形成ができる。他方、バルク体としては焼結法により良好な電気あるいは磁気特性を有する電子セラミックス材料が得られる。しかし、これら薄膜・バルク様の中間に位置する数 $\mu$ mから数百 $\mu$ mの厚さをもつ電子セラミックス材料は、従来技術の延長線上ではなかなか良質なものを高速で得ることができなかった。

最近、明渡ら<sup>1)</sup> は結晶性微粒子をエアロゾル化し、これを高速ジェットに乗せて基板に堆積させるエアロゾル・デポジッション(AD)法を開発し、この手法が上述の電子セラミックス厚膜を得る優れた手法であることを示した。AD法による電子セラミックス厚膜形成技術は、現在NEDOプロジェクト(ナノレベル電子セラミックス材料低温成形・集積化技術プロジェクト)として基礎から応用にわたる広い領域で詳細な検討がなされている。我々もAD法の優れた特長に着目し、この手法で電子セラミックス厚膜を形成することで、いくつかの光デバイスの開発を試みている。

本報では、我々の研究を中心として、結晶性微粒子を室温で高速にボンディング制御して得た電子セラミ

ックス厚膜材料とその応用について述べる。

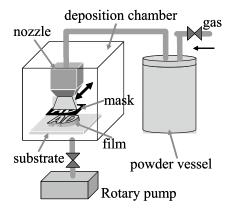

# 2. AD法

図1に、AD法による電子セラミックス厚膜形成の基本構成を示す。概ねサブミクロン程度の大きさをもつ結晶性微粒子を powdervessel 中に入れ、N2などのガスと共にエアロズル化する。このエアロゾルは、数Pa 程度の真空に引かれたチャンバーへ導かれ、先端がスリット状に加工されたノズルから高速ジェットとして基板上に吹きつけることで結晶性微粒子を堆積する。この成膜機構は、常温衝撃固化現象と呼ばれ、圧力差によって音速程度まで加速された結晶性微粒子が、基板衝突時のエネルギーによって粉砕し、その際のメカノケミカル反応によって局所的に活性化することで高密度の薄膜が形成されると考えられている。より詳細には、粒子の運動エネルギーが、粒子と基板と

図1 AD 法の基本構成

の衝突による局所的な熱エネルギーに交換されて基板と粒子間あるいは粒子同士の結合に至ると考えられているが、そのエネルギー交換のメカニズムは明らかにされていない<sup>2)</sup>。特に、成膜直後の膜の結晶性が、原料となる粒子の結晶性が残ったものであるか、粒子が衝突から発生したエネルギーによって融解されて再結晶化したものであるかはよく分かっておらず、これがよい厚膜試料を得るキーポイントといえる。

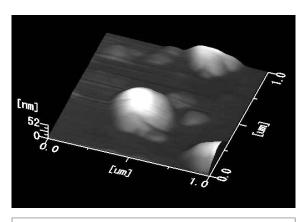

この成膜機構を明らかにするため、我々は、直径 500nm の粒径のよくそろった  $SiO_2$ 粒子を Si 基板に AD 法で衝突させた場合の粒子形状変化を調べた。図 2 は基板に形成された初期段階の膜の AFM イメージである。この図から分かるように、基板に付着した粒子は滑らかな表面を持っており、基板に衝突して粉砕された小粒子が基板に付着されたものとは判断し難い。この結果からは、 $SiO_2$ 粒子は Si 基板と衝突した際のエネルギーによって融解されて基板上に付着形成されたように思われる。一方、図 3 は、基板に形成さ

51.0 nm 43.0 nm 27.0 nm 27.0 nm 19.0 nm 11.0 nm 120.0 nm 240.0 nm 380.0 nm 480.0 nm

図 2 Si 基板との衝突によって付着した SiO<sub>2</sub>粒子 (直径500nm)

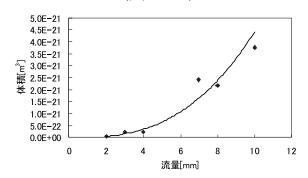

図3 Si 基板との衝突によって付着した SiO<sub>2</sub>粒子の 体積とガス流量との関係

れた粒子の体積を搬送ガスの流量に対してプロットしたものである。基板に付着形成された粒子の体積は流量に対して二次関数的に比例している。搬送ガスの流量は粒子の速度に直接比例し、粒子の運動エネルギーは流量(あるいは速度)の二乗に比例するので、付着した粒子の体積はその運動エネルギーに直接比例していることを示唆している。これらの簡単な実験結果からは、AD成膜の機構は粉砕された微粒子の再付着より、粒子の融解と結晶化によると考えられる。この成膜機構はエアロゾル化した粒子の種類や相手方基板の種類によっても変化すると思われ、今後詳細な検討が必要であるといえる。

現時点で、よい膜を得る観点から様々な基礎的検討が行われているが、結晶性回復のためのポスト熱処理を許す応用については、AD法は極めて魅力的手法であることは事実である。実際、この手法による成膜レートは他の薄膜形成手法を驚愕するほど早く、かつ得られる厚膜試料の密度はバルクの90%以上にも達する。以下では成膜後の熱処理を念頭に置いたいくつかの応用について紹介する。

# 3. AD法による電子セラミックス厚膜の形成

#### 3.1 磁性ガーネット厚膜

透明強磁性体として知られるイットリウム鉄ガーネット  $(Y_3Fe_5O_{12},YIG)$  などの磁性ガーネット材料は、光通信アイソレータや、後述する磁気光学効果を利用した空間光変調器などで用いられる重要な光磁気材料である。

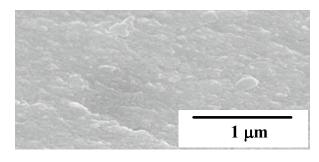

我々は、平均粒径500nmのビスマス置換イットリウム鉄ガーネット( $Bi_{0.5}Y_{2.5}Fe_5O_{12}$ , Bi:YIG) 微粒子を用いて、AD 成膜を試みた。その結果、② 4 に示すように極めて緻密な Bi:YIG 厚膜が得られることが分かった。また、② 5 に示すように、成膜直後であっても膜の透光性は高い。この際の成膜レートは 1  $\mu$  m/min

図 4 AD 成膜した Bi:YIG 厚膜の破断面 SEM 像

図5 AD 成膜した Bi:YIG 厚膜の透光性

図 6 AD 成膜した Bi:YIG 厚膜の磁気光学特性

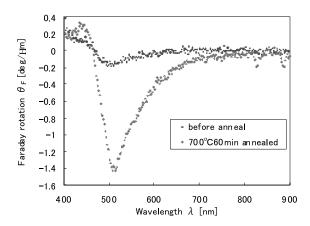

以上であり、アイソレータに要求される厚膜も現実的な時間スケールで得られるといえる。現時点で成膜条件が最適化されていないため、AD 成膜直後のBi:YIG 厚膜には歪導入等による結晶性の劣化が認められるが、ポスト熱処理を施すことにより、図6に示すようにスパッタ法などで得られるBi:YIG 膜に匹敵する磁気光学特性を示す。

## 3.2 マルチフェロ電子セラミック厚膜

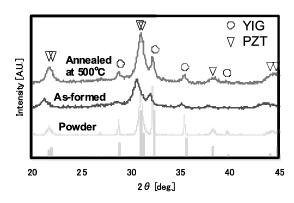

AD法の魅力の一つは、比較的低い温度でセラミックス厚膜が得られることにある。これは、強磁性と強誘電性が共存するマルチフェロ薄膜材料を得る点から魅力あるものといえる。マルチフェロ材料を得る方策の一つに、強磁性材料と強誘電材料を複合化したコンポジット材料があるが、強磁性材料と強誘電材料の形成温度に差があり、これが異相の発生を引き起こすことから現時点で利用可能なものはなかった。AD法は出発時点で結晶性微粒子を利用するので、このような難点のない成膜技術といえる。我々は、PZT 結晶性微粒子と、Bi:YIG 結晶性微粒子とを混合したエアロゾルを用いて AD 成膜を試みた。その結果、図7に示すように、Bi:YIG のガーネット相と PZT のペロブスカイト相が明瞭に共存する厚膜試料を得ている。こ

図 7 PZT/YIG 複合パウダー及び AD 膜の XRD パタ ーン

の厚膜試料の飽和磁化は、本来の Bi:YIG がもつ飽和磁化のオーダにあり、強磁性が保存されている。現在、強誘電性・圧電性の観点から膜特性を調べている。仮に室温で強磁性と強誘電性が保存されていれば、両者の間に結合も期待され、電界(磁界)で磁化(電気分極)を制御できる室温マルチフェロ材料が得られるものと考えられる。

# 4. AD成膜電子セラミックス厚膜の応用

#### 4.1 磁気光学効果を用いた空間光変調器

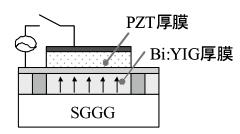

AD 成膜電子セラミックス厚膜の応用として、PZT膜による圧電効果によって Bi:YIG 膜の磁化方位を制御するタイプの空間光変調器 (SLM) を開発している。 SLM はプロジェクタなどに利用されているマイクロディスプレイであるが、最近、高速で動作するデバイスの実現が熱望されている。我々は、磁性体中の磁化がnsオーダの速度でスイッチングすることに着目し、磁気光学 (MO) 効果を利用した SLM を開発している。磁化方位制御は一般には電流による磁界を利用するが、磁化方位を電圧で制御できれば発熱などの難点のないデバイスが得られるといえる。図8に試作したデバイスの構成を示す。Bi:YIG 膜上に AD 法により

図 8 PZT 厚膜の圧電効果で Bi:YIG 膜中の磁化方位 を制御する磁気光学方式 SLM の基本構成

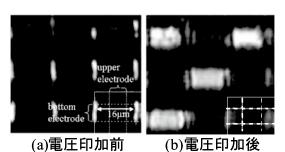

PZT 厚膜を形成し、圧電駆動による磁化方位制御を試みた。その結果、図9に示すように磁化方位が反転した領域が明るく観測され、AD 成膜 PZT 膜で動作する光マイクロデバイスが得られている。

図9 圧電駆動による磁化方位制御

#### 4.2 マルチモードPLZT光導波路

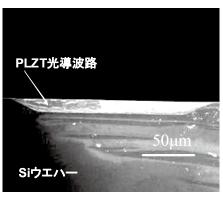

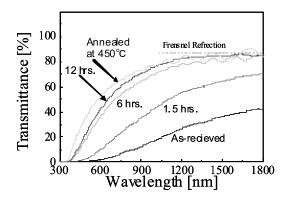

Fibertothehome (FTTH) の進展に伴って、家庭で利用される安価な光スイッチの開発が望まれている。我々は、ホログラム光フィルターと光スペックルパターン変調を組み合わせた光クロスコネクト装置を提案し、原理動作確認を行った。この原理に基づく小型光スイッチの開発には、電気光学 (EO) 効果を持つマルチモード光導波路が不可欠であり、このために AD法を用いた PLZT 厚膜光導波路開発を行っている。図10に示すように、AD成膜条件を選ぶことで、1.5μm 波長帯で光損失の極めて少ない PLZT 厚膜が得られている。図11はこの膜を用いた埋め込み型光導波路の断面写真である。緻密な PLZT 厚膜光導波路が形成できることが分かっており、この光導波路を用いた小型固体光スイッチの開発が進んでいる。

本研究の一部は、NEDOナノ電子セラミックスプロジェクト並びに文部科学省革新技術開発事業の援助を受けて行ったものである。Bi:YIG 微粒子を提供していただいたホソカワミクロン(株)に深謝する。

#### 参考文献

- 1) J. Akedoand M. Lebedev, J. Crystal Growth, vol. 235 (2002) 415.

- 2) 明渡純, 杉本諭, 日本応用磁気学会誌, vol. 29 (2005) 20.

#### Caption

Fig. 1 Fundamental setup of the AD system.

Fig. 2 AFM image of the SiO<sub>2</sub> particles (500 nm in diameter) deposited onto a Si substrate

図10 AD 形成した PLZT マルチモード光導波路

図11 AD 形成した PLZT 膜の透過率波長スペクトル。 図中の時間は PLZT 粉体のミリング時間

- Fig. 3 Volume of SiO<sub>2</sub> fine particles deposited onto a Si substrate vs. gas flow.

- Fig. 4 Cross-sectional SEM image of the AD-formed Bi:YIG thick film.

- Fig. 5 Transmissivity of the AD-formed Bi:YIG thick film.

- Fig. 6 Wavelength spectrum of the Faraday rotation angle of the AD-formed Bi:YIG film.

- Fig. 7 XRD pattern of the PZT/YIG composite power and its AD-formed film.

- Fig. 8 Fundamental structure of magneto-optic SLM, in which the direction of magnetization is controlled by the piezoelectric effect of the PZT thick film deposited onto the Bi:YIG film.

- Fig. 9 Control of the magnetization direction via piezoelectric effect.

- Fig. 10 Cross-sectional SEM image of the PLZT multimode optical waveguide formed by the AD method.

- Fig. 11 Wavelength spectra of transmissivity of the AD-formed PLZT films, where the milling time of starting PLZT power is taken as a parameter.